#### **EE 213 FINAL EXAM**

#### 2017-2018

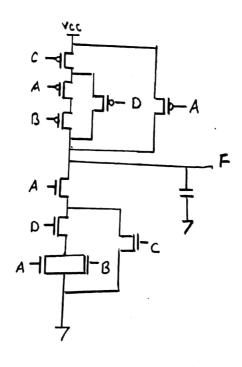

Q1) (30p) Write the expression of the point F for the given circuit below.

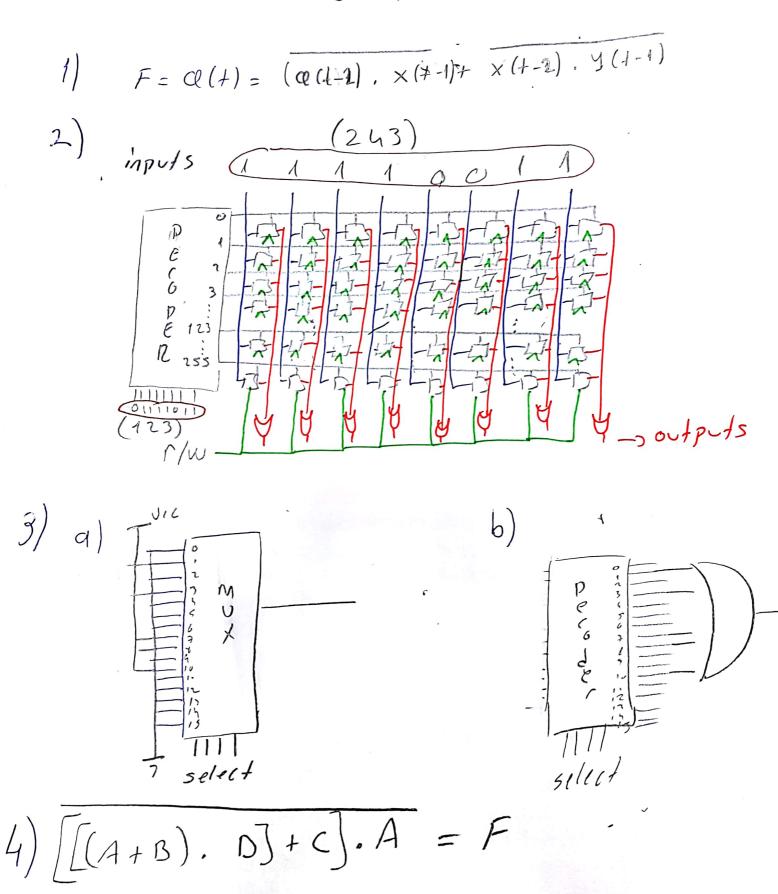

Q2) (25p) Design a 8x8 RAM and declare the necessary input, selections, control bits etc... on your design such that it will write the value of 243 to the address of "123".

Q3) Design the Circuit for  $F = \sum (1,3,7,8,10)$

- a) (15p) By using oly one multiplexer

- b) (10p) By using only one decoder

**Q4) (20p)** Write the unsimplified expression for the gicen Complementary Metal Oxide Semiconducter (CMOS) circuit below.

**©Good Luck ©**

# EE 213 FINAL SOLUTIONS

| Name Surname : | ID: |

|----------------|-----|

|                |     |

## EE 213 Digital Design

#### **FINAL EXAM**

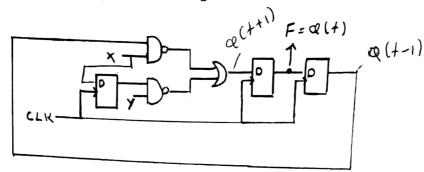

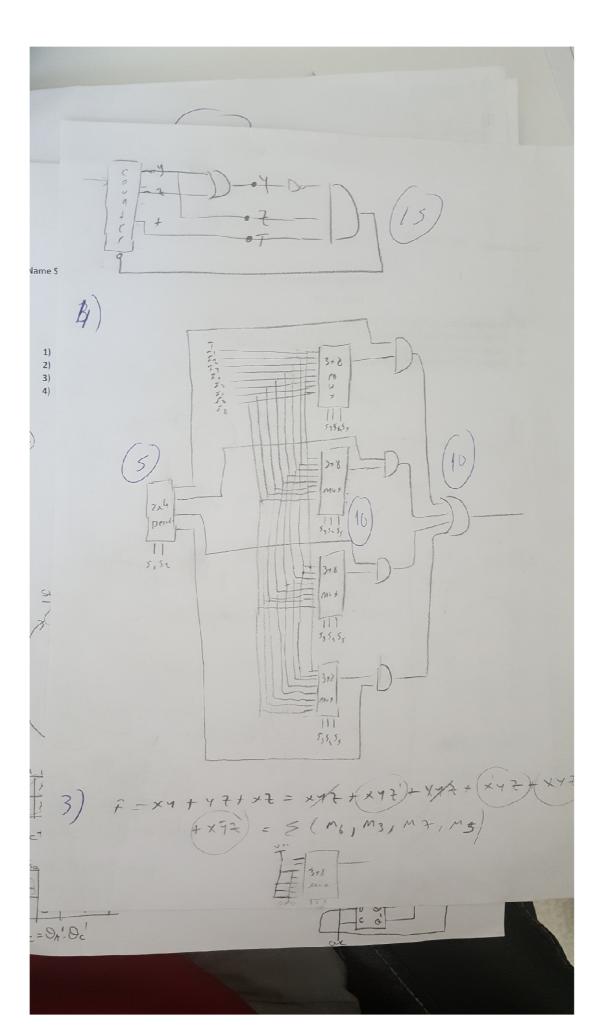

- 1) Design the circuit for Q(t+1)=Q(t-1)+Q(t)

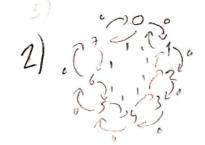

- 2) Design a counter that counts as 0,1,4,2,5,6, 0,1,4,2,5,6, ...

- 3) Design a circuit that implements F = xy + yz + xz by using a multiplexer

- 4) Design a 5x 32 multiplexer by using four 3x 8 multiplexer.

Name Surname: SOLUTIONS ID: **EE 213 Digital Design** FINAL EXAM 1) Design the circuit for Q(t+1)=Q(t-1)+Q(t)2) Design a counter that counts as 0,1,4,2,5,6, 0,1,4,2,5,6, ... 3) Design a circuit that implements F = xy + yz + xz by using a multiplexer 4) Design a 5x 32 multiplexer by using four 3x 8 multiplexer. Q(14) 0 0 0 01 0 00

# Name Surname : 11.12.2021

Student ID :

#### 2020-2021

#### **FALL**

#### **EE 213 FINAL EXAM**

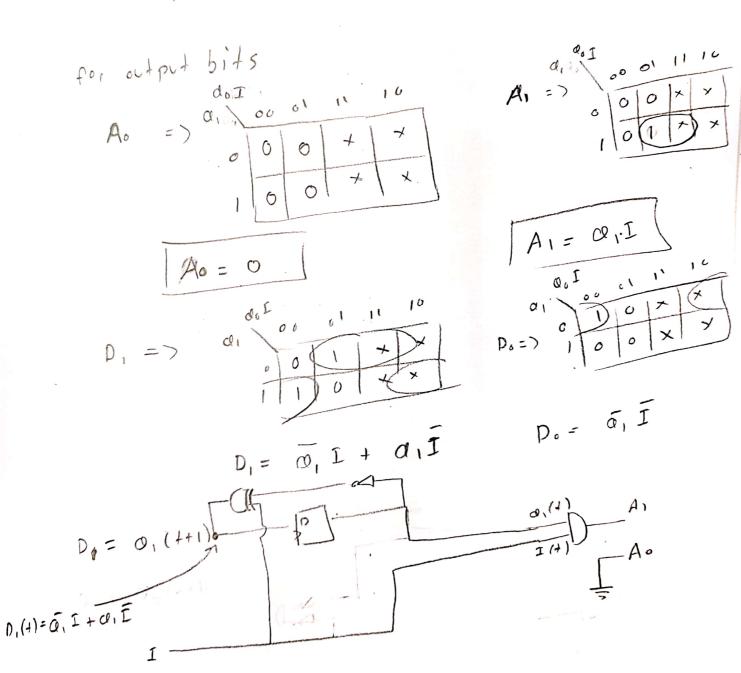

**Q1) a) 34p** Please design and DRAW the circuit of output for the REDUCED state table (if it is reducable) form of the given state table given below.

| Present | Next      | Next      | Output    | Output    |

|---------|-----------|-----------|-----------|-----------|

| State   | State     | State     | (input=0) | (input=1) |

|         | (input=0) | (input=1) |           |           |

|         |           |           |           |           |

| 00      | 11        | 10        | 01        | 01        |

| 01      | 01        | 10        | 11        | 11        |

| 10      | 10        | 01        | 00        | 10        |

| 11      | 01        | 10        | 11        | 11        |

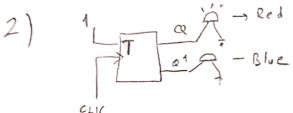

**Q2) 33 p** Please design a circuit that has a red led and a blue led and simulates a police light (i.e : The red led turns on and off periodically and it gives light when the blue one doesn't, then it turns off when the blue one turns on.)

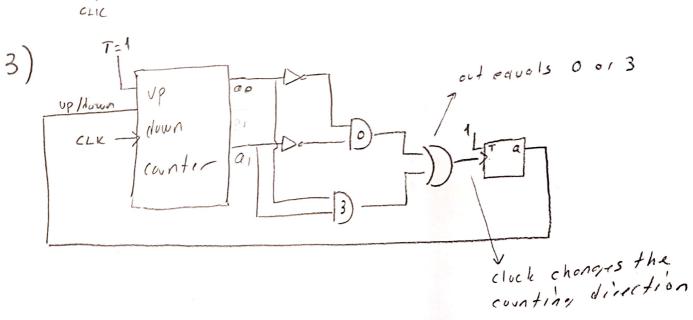

**Q3) 33 p** Design a counter that counts upto 3 and back down to 0 such as; 0,1,2,3,2,1,0,1,2,3,2,1,0...

Name Surname:

SOLUTIONS

11.12.2021

Student ID

2020-2021

#### **FALL**

#### **EE 213 FINAL EXAM**

Q1) a) 34p Please design and DRAW the circuit of output for the REDUCED state table (if it is reducable) form of the given state table given below.

|     | Present<br>State | Next<br>State<br>(input=0) | Next<br>State<br>(input=1) | Output<br>(input=0) | Output<br>(input=1) |

|-----|------------------|----------------------------|----------------------------|---------------------|---------------------|

| O   | 00               | 210                        | 10                         | 01 60               | 0100                |

| 1   | -01              | -01                        | 10                         | 2101                | 21-0-               |

| 2   | 10               | 10                         | 0100                       | 00                  | 10                  |

| 3 - | -11              | -01                        | -10                        | 11                  | -1.1                |

Q2) 33 p Please design a circuit that has a red led and a blue led and simulates a police light (i.e : The red led turns on and off periodically and it gives light when the blue one doesn't, then it turns off when the blue one turns on.)

Q3) 33 p Design a counter that counts upto 3 and back down to 0 such as; 0,1,2,3,2,1,0,1,2,3,2,1,0...

# SOLUTIONS

1) line I and 3 are some, line 3 will be conselled and all II's will be at an remain, parts

Then, line a and I become some and line I will be concelled, and all at's will be ac an remaining parts, new state table becomes

| ρs | N S<br>1=0 | NS<br>I=1 | 1:0 | Ou!<br>  I=1 |

|----|------------|-----------|-----|--------------|

| 00 | 01         | 10        | 00  | 00           |

| 10 | 10         | 00        | 00  | 16           |

Extending it;

| PS-I | NS  | Out<br>AL AO |

|------|-----|--------------|

| 000  | 010 | 00           |

| 001  | 10  | 0 0          |

| 010  | XX  | XX           |

| 611  | XX  | ×Х           |

| 100  | 0.0 | 00           |

| 101  | 00  | 10           |

| 110  | ××  | * * .        |

| 11)  | ××  | * * '        |

Name Surname: SOLUTIONS

ID

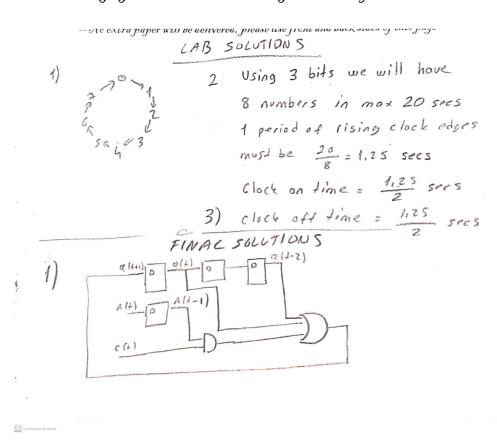

## EE 213 LAB Exam

10.01.2022

1) Please draw the state diagram of a 3 bits counter such that it will give the outputs of one period in 20 seconds, and shows exactly one period on the screen.

- 2) To see the outputs exactly as above what value should the clock on time be adjusted to?

- 3) To see the outputs exactly as above what value should the clock off time be adjusted to?

# **EE 213 FINAL EXAM**

- 1) Draw the circuit for Q(t+1)=Q(t)+A(t-1).C(t)+Q(t-2)

- 2) Draw the state diagram of a 3 bits up/down counter.

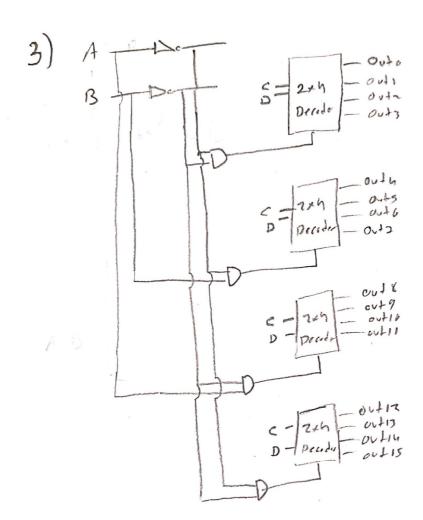

- 3) Design a 4x16 decoder using four 2x4 Decoder

--No extra paper will be delivered, please use front and back sides of this page-